#### ■受領No.1432

# SiC デバイス信頼性確保に向けた SiC エピタキシャル層 キャリア寿命測定

代表研究者 加藤 正史 名古屋工業大学 准教授

# Measurements of carrier lifetime in SiC epitaxial layers for ensuring reliability of SiC devices

Principal Researcher

Masashi KATO,

Nagoya Institute of Technology Associate Professor

SiC デバイスの信頼性確保のために、バイポーラ劣化を抑制可能なキャリア寿命の指針とその測定法をシミュレーションおよび実験的に検討した。その結果、実験的に得られるキャリア寿命測定値において、バイポーラ劣化を抑制に必要な条件を推定することができた。一方で、その条件を満たす値を得るために、キャリア寿命の制御を試みたがいずれの制御手法を施しても必要な値を満たすことができなかった。したがって、バイポーラ劣化の抑制にはキャリア寿命の制御だけでは充分でないことが明らかになった。

In order to ensure the reliability of SiC devices, the guideline of the carrier lifetime that can suppress bipolar degradation and its measurement method were investigated by simulation and experiment. We estimated the experimental value necessary to suppress bipolar degradation in the carrier lifetime measurements. On the other hand, we attempted to control the carrier lifetime to obtain a value that satisfied the estimated value, but could not satisfy the estimated value by any of the control methods. Therefore, it is clear that carrier lifetime control alone is not sufficient to suppress bipolar degradation.

## 1. 研究内容

#### 1. はじめに

SiC デバイスでは、長期信頼性を確保するためにバイポーラ劣化と呼ばれる現象を抑制することが求められている。このバイポーラ劣化が起こる原因は、基底面転位の拡大によるシングルショックレー積層欠陥(1SSF)であるとされている。そして、このバイポーラ劣化の駆動力は、基底面転位での電気伝導キャリアの再結合である。したがって、基底面転位付近でのキャリアの再結合を抑制すれば、バイポーラ劣化の抑制が可能である。ここで SiC デバイスに用いられる厚さ 10 μm 程度

のエピタキシャル層の内部においては、基板中の基底面転位の方向をエピタキシャル層/基板界面で転換することで、基底面転位をほぼ無くす技術が確立されている。一方で、基板中は数多くの基底面転位が存在するため、そこにキャリアが到達してしまうと 1SSF へと拡張し、エピタキシャル層にまで拡大し劣化が起こる。したがって、バイポーラ劣化を抑制するためには、エピ層内でのキャリア寿命が短いことが必要である。しかしながら、10 μm 程度のエピタキシャル層厚では、表面と基板の存在により、エピ層内のキャリア寿命の測定は通常困難である。そこで本研究では、10 μm

のエピタキシャル層で要求されるキャリア寿命の 指針とその測定方法について、シミュレーション と実験により検討を行った。

#### 2. シミュレーション

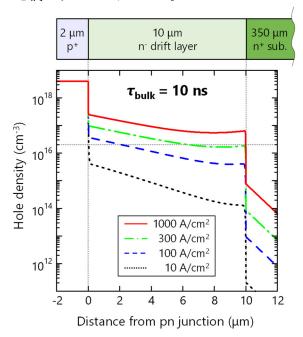

これまでの研究により、SiC pn ダイオードを動作させたとき、アノードから注入される正孔密度がエピ層と基板の界面で  $2\times10^{16}$  cm<sup>-3</sup> に達するとバイポーラ劣化が起こることがわかっている[1]。そこで一次元半導体デバイスシミュレータであるAFORS-HET [2]を用いて、厚さ  $10\,\mu m$ 、ドナー密度  $10^{16}$  cm<sup>-3</sup>のドリフト層を有する SiC pn ダイオードの順方向動作のシミュレーションを行った。このとき、ドリフト層のキャリア寿命( $\tau_{bulk}$ )を  $10\,ns$ とすると、図 1 に示すような電流密度に対する正孔密度の分布が計算できた。電流密度  $300\,A/cm^2$  の場合、界面で正孔密度が  $2\times10^{16}\,cm^{-3}$  以下になっている。したがって、 $300\,A/cm^2$  の定格電流のデバイスでは、ドリフト層のキャリア寿命は  $10\,ns$  以下でなければならないことがわかった。

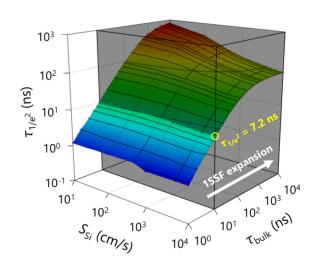

10 μm のエピタキシャル層のキャリア寿命が 10 ns 以下であることを実験的に保証するためには、 エピタキシャル層内部でのみキャリアが生成され る測定をする必要がある。そこで光の侵入深さが 1 μm 程度である波長 266 nm のパルスレーザー励 起によりキャリア寿命測定を行った。用いた手法 はマイクロ波光伝導度減衰(μ-PCD)法であるが、 実験的に得られる値には表面再結合の影響を含ん でしまう。そのため、まずは実験結果の解釈にお いて表面再結合の影響を排除するため、u-PCD 信 号を偏微分方程式を用いて計算した。ここで、基 板における再結合は、C 面の表面再結合速度 SC で近似した。μ-PCD 信号のピークを1とし、信号 が 1/e から  $1/e^2$  に減少するまでの時間を  $1/e^2$  ライ フタイム  $(\tau_{1/e}^2)$  と定義した。図 2 は、 $S_{C}=10^4$  cm/s における Si 面の表面再結合速度  $S_{Si}$  と  $\tau_{bulk}$  および  $au_{1/e}^2$  の関係を示したものである。この結果から、 全ての  $S_{\text{Si}}$  において  $\tau_{1/e}^2$  < 7.2 ns であれば  $\tau_{\text{bulk}}$  < 10 ns を満たすことがわかった。

図 1. 厚み  $10 \mu m$ 、ドナー濃度  $10^{16} cm^{-3} o$ ドリフト層を有する pn ダイオードにおける正孔密度分布。ドリフト層のキャリア寿命は 10 ns、注入電流密度は  $10-1000 A/cm^2$  とした。

図 2.  $\tau_{1/e}^2$ の SSi および $\tau_{bulk}$ への依存性。灰色で示した領域は $\tau_{bulk}$ が 10ns 以上であり、1SSF の拡張が可能である条件である。

#### 3. 実験結果

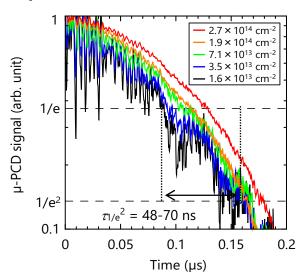

図 3 に厚さ 10  $\mu$ m、ドナー密度  $10^{16}$  cm<sup>-3</sup> の エピタキシャル層を有するサンプルに対して、様々な入射光子密度で測定した $\mu$ -PCD 減衰曲線を示す。いずれの測定条件においても $\tau_{1/e}^2$ は 48-70 ns の範囲に収まり、7.2 ns よりかなり大きいことがわかる。

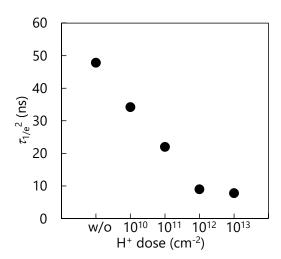

$au_{\text{bulk}}$ を短くするために、0.95~MeV の  $H^+$ 照射を同じウェハから切り出したエピタキシャル層に施した。図  $4~\text{は測定された}\, au_{1/e}^2$ の  $H^+$ 照射量依存性を示している。 $10^{13}~\text{cm}^{-2}$ の  $H^+$ 照射量で 7.8~ns という最小の $au_{1/e}^2$ が得られたが、この $au_{1/e}^2$ は 7.2~ns よりまだ長い。より高い密度で $H^+$ を照射した場合、 $\mu$ -PCD 信号が得られないほどエピタキシャル層の品質が劣化してしまった。

図 3. 266 nm パルス励起レーザーの入射光子密度 を変化させた場合の厚み  $10~\mu m$ 、ドナー密度  $10^{16}~cm^{-3}$  を有するエピタキシャル層から得られた  $\mu$ -PCD 減衰曲線。

他の手法として電子線照射、もしくは 1850℃でアニールすることにより点欠陥の高温での熱平衡濃度[3]を利用することでキャリア寿命の減少も試みた。しかしながら、いずれの手法によっても τ1/e²が 7.2 ns 以下になることはなかった。したがって、実験的にはエピタキ

シャル層のキャリア寿命をバイポーラ劣化を 抑制可能な値まで減少させることはできなかった。

### 4. まとめ

本研究によりエピタキシャル層のキャリア寿命の制御のみでバイポーラ劣化を抑制するための数値目標が明確になった。ただし、いかなる手法を用いても実験的にその目標値までキャリア寿命を減少させることはできなかった。したがって、バイポーラ劣化の抑制にはエピタキシャル層のキャリア寿命の制御のみならず、既報[4]にあるようなバッファ層の導入などと組み合わせることが必要になると考えられる。

- [1] T. Tawara et al., (2018) J. Appl. Phys. 123, 025707.

- [2] R. Varache et al., (2015) Sol. Energy Mater Sol. Cells 141, 14-23.

- [3] B. Zippelius et al., J. Appl. Phys. 111, 033515(2012).

- [4] T. Tawara et al., J. Appl. Phys. 120, 115101(2016).

図 4. H+照射を施した厚み 10 mm、ドナー密度  $10^{16} \text{ cm}^{-3}$ のを有するエピタキシャル層に対する $\mu$ -PCD減衰曲線から得られた  $\tau_{1/e}{}^2$ 。測定に使用した入射光子密度は  $10^{14} \text{ cm}^{-2}$  である。

自然科学・工学研究部門:1年助成

# 2. 発表 (研究成果の発表)

"4H-SiCバイポーラ劣化抑制に向けたドリフト層内のキャリアライフタイムの検討"三井 俊樹、加藤 正史、2021年第82回応用物理学会秋季学術講演会[10p-S202-7] (オンライン) 2021年09月 応用物理学会

"4H-SiCバイポーラ劣化抑制に求められるドリフト層内キャリアライフタイムの評価"三井 俊樹,加藤 正史、先進パワー半導体分科会第8回講演会(オンライン) 2021年12月月 応用物理学会先進パワー半導体分科会

"Discussion on carrier lifetime control in a drift layer of 1.2 kV class 4H-SiC devices for suppression of bipolar degradation", Toshiki Mii, Shunta Harada, Hitoshi Sakane, Masashi Kato, 19th International Conference on Defects-Recognition, Imaging and Physics in Semiconductors (オンライン) 2022年8月(投稿中)